# Design & Verification Challenges for 3G/3.5G/4G Wireless Baseband MPSoCs

Michael Speth Herbert Dawid Frank Gersemsky

Infineon Technologies AG Duisburg, Germany

### Outline

- challenges of 3G / 4G modem design

- data throughput

- □ latency

- configurability

- wireless standards: a nightmare for system verification

- keys to success:

- architecture

- methodology

- □ team-setup

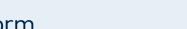

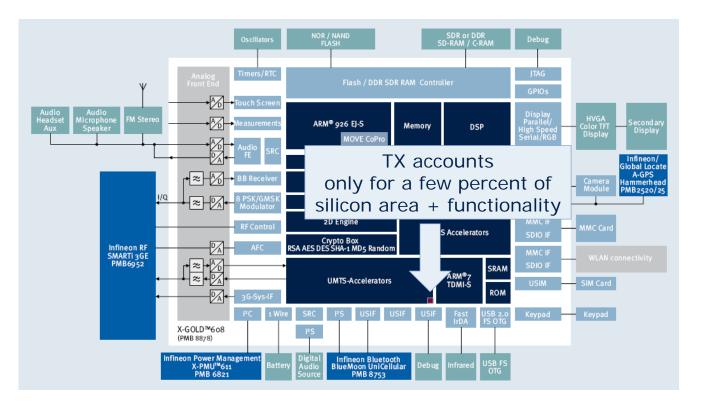

### State of the Art Cellphone Platform

### A Heterogeneous Application Specific Multi-Processor SoC

03.07.2008

Copyright  $\ensuremath{\textcircled{O}}$  Infineon Technologies 2008. All rights reserved.

```

Page 3

```

(infineon

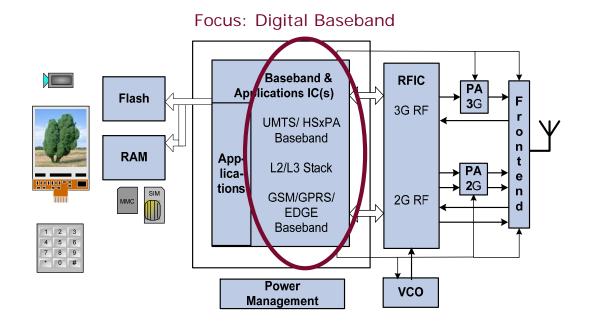

## Example: Infineon MP-EH Platform

### Why Dedicated Wireless MPSoCs?

- Thought Experiment: Modern digital cellular baseband

- 20 GOPs peak signal processing demand (active)

- 0 GOPs computational demand (standby, paging)

- State of the art battery with 1400 mAh capacity

- What if we use 2 general purpose processors (like the ones in your desktop PC), assuming they would be powerful enough?

- 60 W peak power consumption

- 20 W standby power consumption

- Result

- □ Active Time: 40 s

- □ Standby Time: 30 min

- We are building SoCs which are 100-1000x more energy efficient than state of the art GP processors and at the same time more efficient, faster, smaller and cheaper

03.07.2008

Copyright © Infineon Technologies 2008. All rights reserved.

Page 5

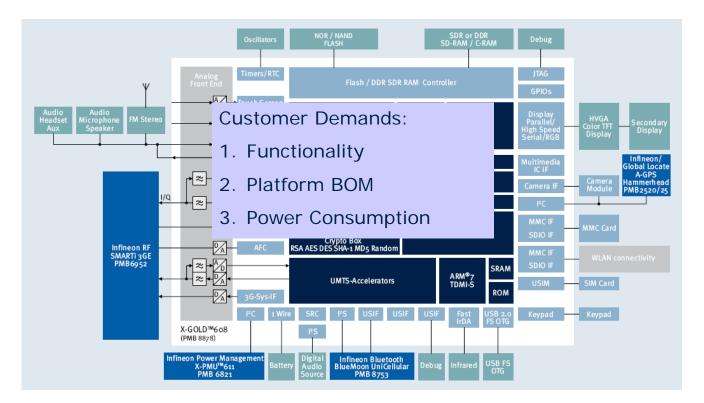

# Throughput

### Wireless Data Rate Evolution

## How to Address the Challenge

- "Shannon beats Moore"

- Increasing gap between chip technology and throughput requirements

- Architecture + Algorithm

- □ 2G: DSP Centric Architectures

- 3.XG: + Dedicated HW Centric Architectures

- □ 4G : + More Efficient Transmission Technology (OFDM)

Throughput requirements are extremely tough

but can be met with state of the art

#### architectures + methodology

Cinfineon

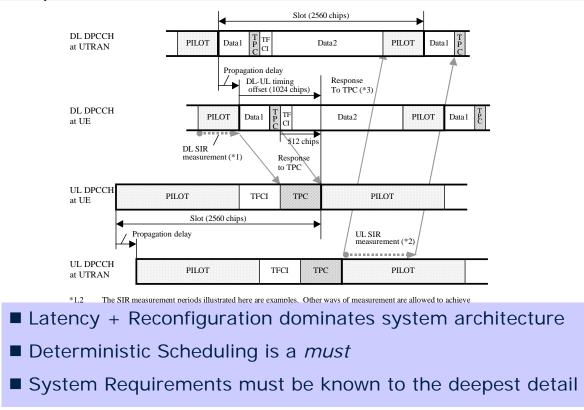

# Latency Requirements

03.07.2008

Copyright © Infineon Technologies 2008. All rights reserved.

Page 9

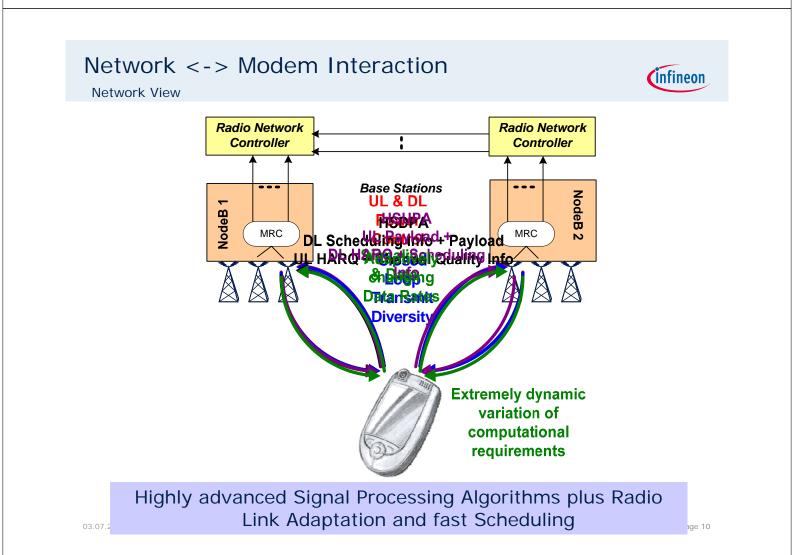

## Network <-> Modem Interaction

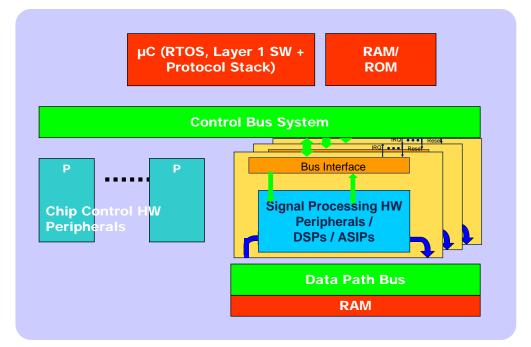

Digital Baseband Architectural View

Example: 3G Power control

(infineon

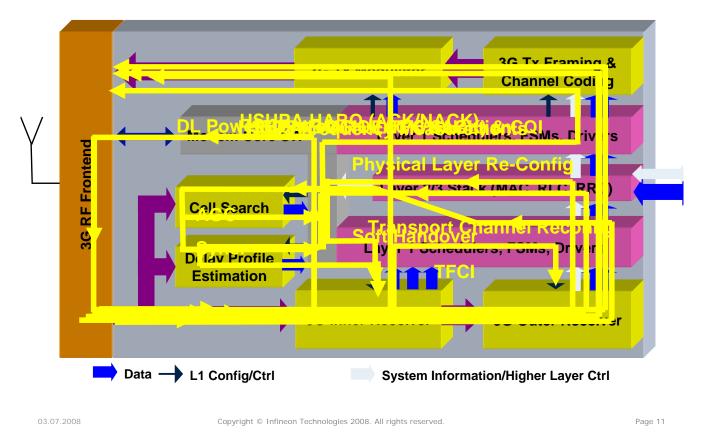

# System Configurability

03.07.2008

Copyright © Infineon Technologies 2008. All rights reserved.

Page 13

(infineon

## Example: UMTS TX

## TX Processing for UMTS Rel. 6

## System Configurability

- 3G Transmitter:

- Well defined serial bit processing

- □ *But*: parameter flow can exceed data-flow

- 3G Receiver: much much more complicated

- Multiple Base Stations, Soft Handover, Transmit Diversity

- □ Multiple Rake Fingers, Receive Diversity

- Complex Reconfigurations

- Additional Neighbor Cell BCH

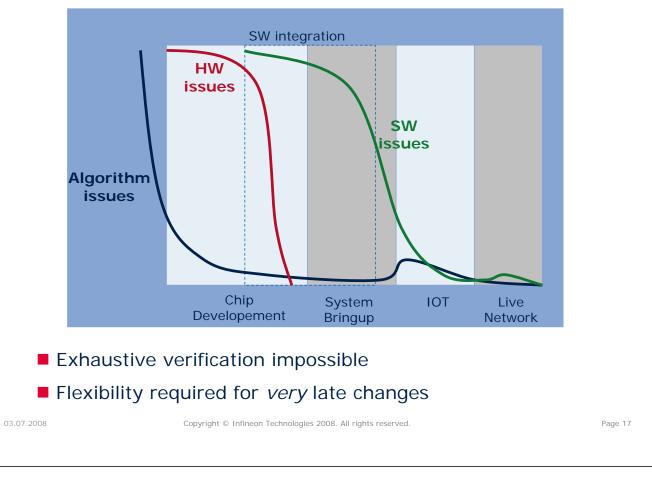

No exhaustive test possible

Even minimum testing leads to thousands of complex test-cases

## System Development and Bringup

(infineon

# Architecture

## System Design Paradigms

#### System Predictability

#### Static real-time scheduling based on Worst Case Execution Times (WCETs)

#### Localized Functionality

Divide and Conquer: Cluster Functionality

- Self-Contained HW & FW Blocks

- $\rightarrow$ Localized Functionality, Lean Interfaces

- $\rightarrow$ Simplified Integration & Verification

- $\rightarrow$ Sometimes Extra HW Needed

#### Performance vs Complexity

Flexibility Where Needed

Algorithm Design: Robust and "As Good As Needed"

#### Limited HW-SW Interaction

■HW-SW Split: Encapsulate Functionality in HW HW-SW Interface Natural Boundary for Function

- Clusters Latency Critical Paths in HW  $\rightarrow$

- $\rightarrow$ Simplified SW Scheduling

- $\rightarrow$ No Critical HW-SW Interactions

## ■Configuration Granularity: UMTS Slot (667 µs) and Frame (10 ms) Boundaries

Simplified Verification  $\rightarrow$

03.07.2008

Copyright © Infineon Technologies 2008. All rights reserved.

Page 19

(infineon

## **Digital Baseband Detailed Architecture**

### Separate functionality into autonomous subsystems

03.07.2008

Copyright © Infineon Technologies 2008. All rights reserved.

Page 22

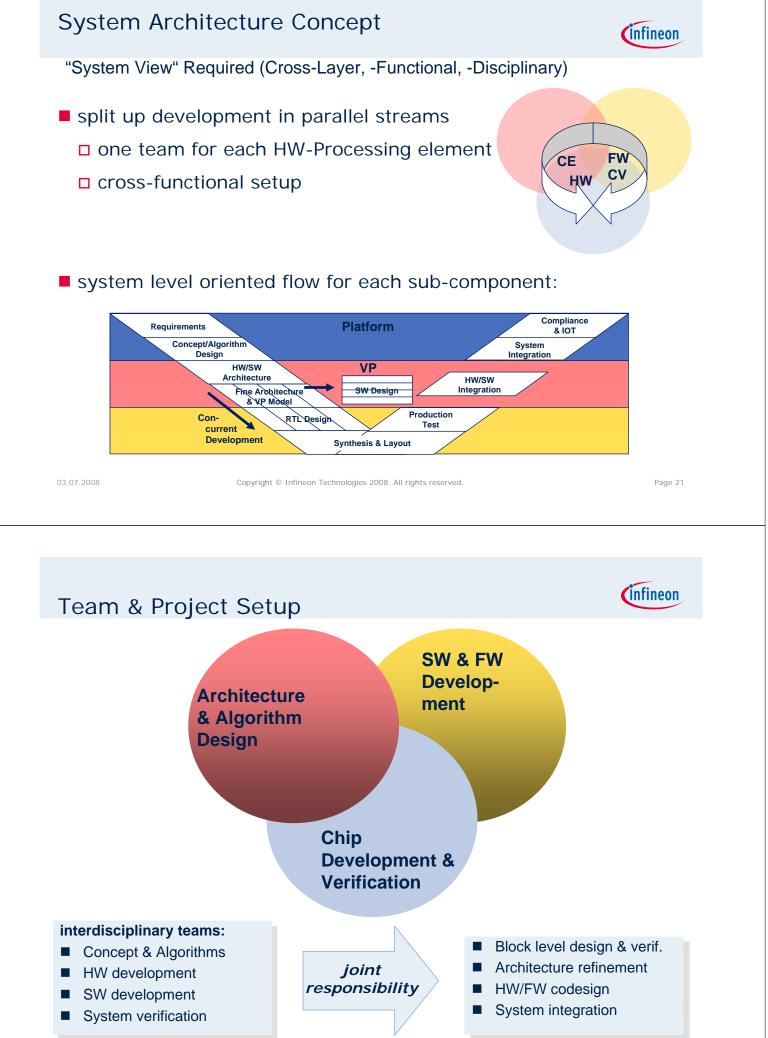

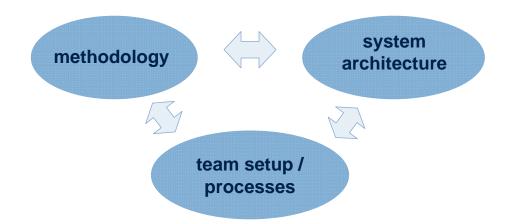

# Methodology

03.07.2008

Copyright © Infineon Technologies 2008. All rights reserved.

Page 23

(infineon

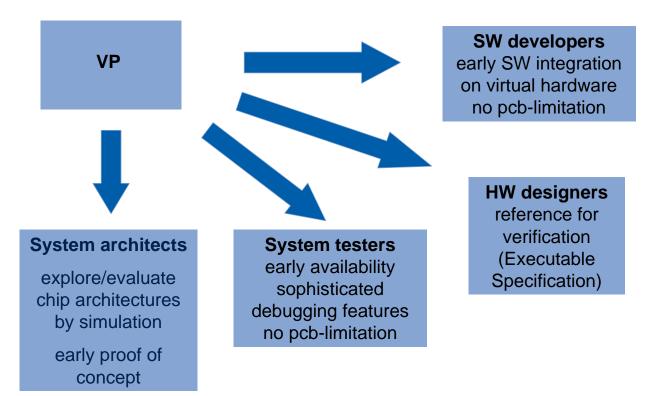

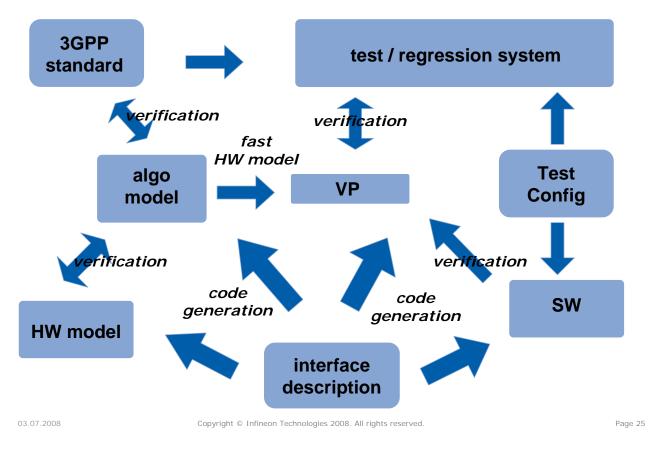

## Key Methodology: Virtual Prototype

03.07.2008

## Methodology: Bridging Levels of Abstraction

- Integrated tool landscape to provide maximum reuse

- Seamless transition between different levels of abstraction

- Platform for cross-functional team interaction

- Provide uniform touch-and-feel throughout all project phases

Cinfineon

## Conclusion

- Greatest challenge:

- System reconfigurability

- Latency critical loops

- Not data-throughput

- Success requires a system-level approach:

- Exhaustive and detailed system knowledge

- Interdisciplinary teams

- Integrated design and verification flow

Copyright © Infineon Technologies 2008. All rights reserved.

Page 27

Cinfineon